# RAPID AUTHENTICATION THROUGH VERIFICATION, VALIDATION, AND MARKING

Mr. Kerry Bernstein, DARPA/MTO Program Manager

NDIA Trusted Microelectronics Workshop

August 17, 2016

# The DARPA solution is to provide a menu of hardware security options that can be selectively applied based on need

|                                |                                          |                |                     | Microelectronics Security Threats |                |                        |                         |  |

|--------------------------------|------------------------------------------|----------------|---------------------|-----------------------------------|----------------|------------------------|-------------------------|--|

|                                | Protection                               | Program        | Loss of information | Fraudulent products               | Loss of access | Malicious<br>insertion | Quality and reliability |  |

| High Government Intervention   | Government-<br>proprietary               | Other          | •                   |                                   |                |                        |                         |  |

|                                | Fine<br>Disaggregation<br>and Transience | TIC<br>(IARPA) | •                   | •                                 | •              | •                      |                         |  |

|                                |                                          | VAPR           | •                   |                                   |                |                        |                         |  |

|                                | Functional<br>Disaggregation             | SPADE          | •                   |                                   |                | •                      | •                       |  |

|                                |                                          | DAHI           | •                   |                                   | •              | •                      |                         |  |

|                                |                                          | CHIPS          | •                   |                                   | •              | •                      | •                       |  |

| High Commercial<br>Sponsorship | Obscuration<br>and Marking               | CRAFT          |                     |                                   | •              |                        | •                       |  |

|                                |                                          | eFuses         | •                   |                                   |                | •                      |                         |  |

|                                |                                          | SHIELD         | •                   | •                                 |                |                        |                         |  |

|                                | Verification<br>and Validation           | IRIS           |                     | •                                 |                | •                      | •                       |  |

|                                |                                          | TRUST          |                     | •                                 |                | •                      |                         |  |

SHIELD, IRIS, and TRUST can help protect against the introduction of fraudulent products and ensure that genuine microelectronics perform only as expected.

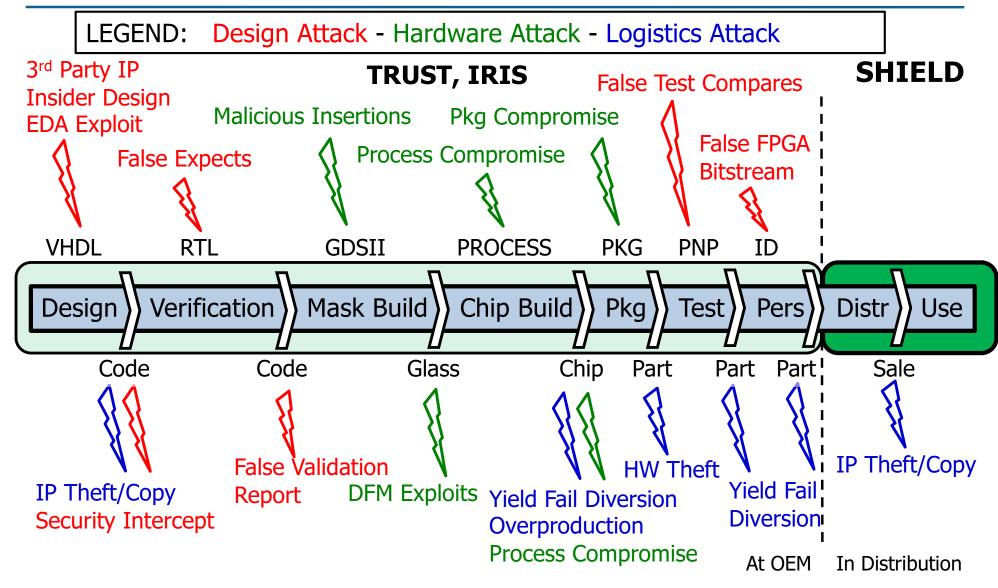

### Hardware-specific exploits, mitigations

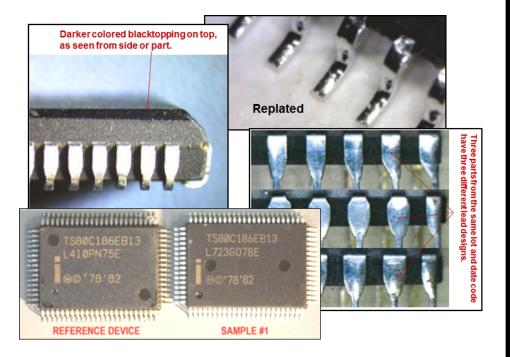

#### **Counterfeits**

Still the original part from OEM:

- Recycled used components

- OEM's fab test failures sold on black market

- Unlicensed fab overproduction

#### **Clones**

A completely different part:

- Copies fabbed in foreign plant

- New design of reverse-engineered components using stolen IP, potentially with altered function

Suspect

Good

Suspect

Good

All images courtesy of NSWC CRANE

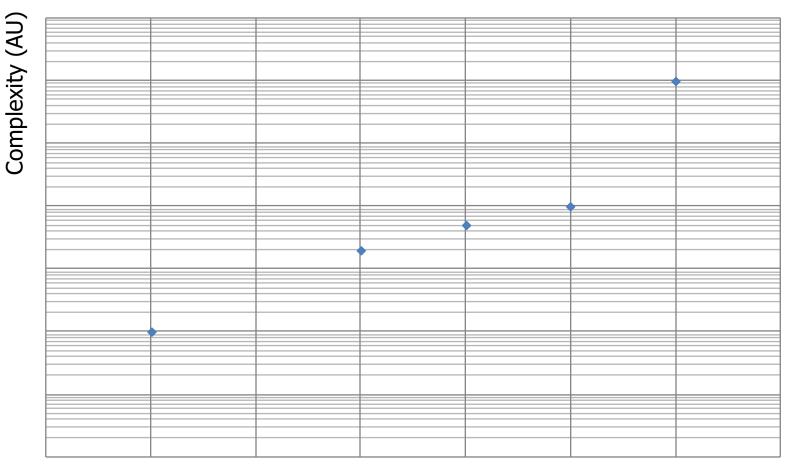

## Trend in reverse engineered + cloned component growth

#### Exemplary high-level clone discoveries collected over past 3 years\*

Original Component Issue Date

Counterfeiter skills for reverse engineering complex components are growing, and tracking Moore's Law

<sup>\*</sup> Developed with B. Hamilton, NSWC Crane

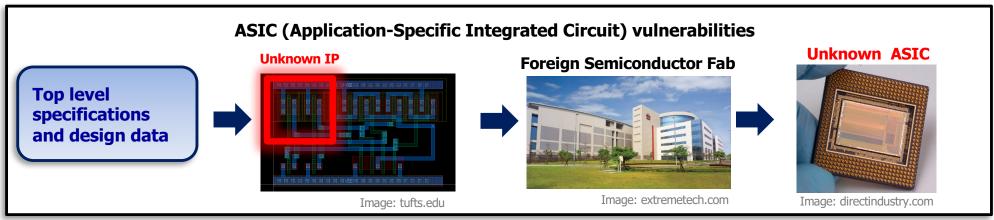

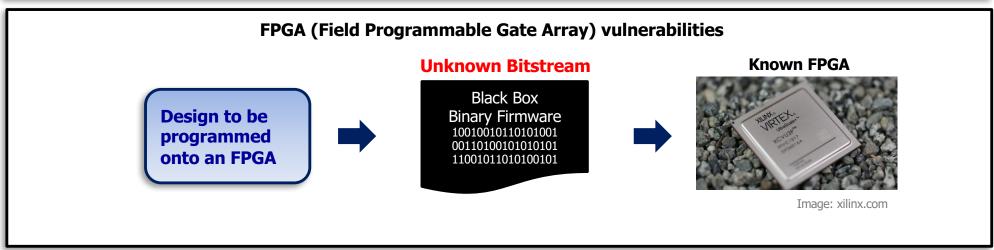

### TRUST in Integrated Circuits

#### Integrated circuits must function as designed – no more, no less

#### The TRUST program addressed these vulnerabilities in four thrusts:

- Trust in fabrication for ASICs

- 2. Trust in design for ASICs

- Trust in FPGAs

- 1. Trust in third-party intellectual property (IP)

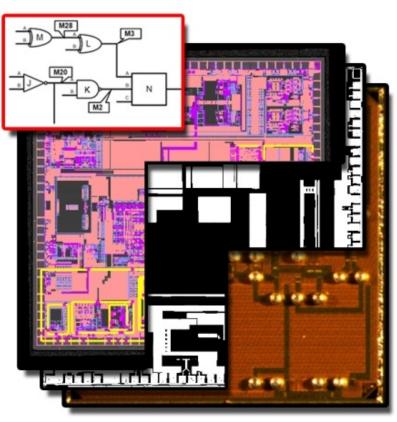

### Integrity and Reliability of Integrated circuitS (IRIS)

#### IC functionality extraction and reliability estimation

#### **Objectives**

- 100% functionality derivation given a limited data sheet and an IC, FPGA or 3<sup>rd</sup> party IP

- MTTF analysis of an IC given limited sample size

- Forensics to identify IC anomalies and determine impact on reliability

#### **Capabilities developed**

- Non-destructive imaging for feature resolution

- Algorithms for pattern recognition and netlist extraction

- Data analytics for functional derivation

- Advanced modeling and simulation techniques for reliability analysis

Artist's rendering of images provided by Air Force Research Laboratory

#### **Virtual Laboratory**

- Designed, developed and debugged test articles for performer analysis

- Evaluated performer techniques for scientific soundness, and results against program metrics

#### **Performers**

BAE Systems

SRI International

USC Information Sciences Institute

Raytheon

Luna (MacAulay Brown)

Orora

R3 Logic

Case Western Reserve Univ.

Georgia Tech

University of Michigan

Boeing

IBM

University of Arkansas

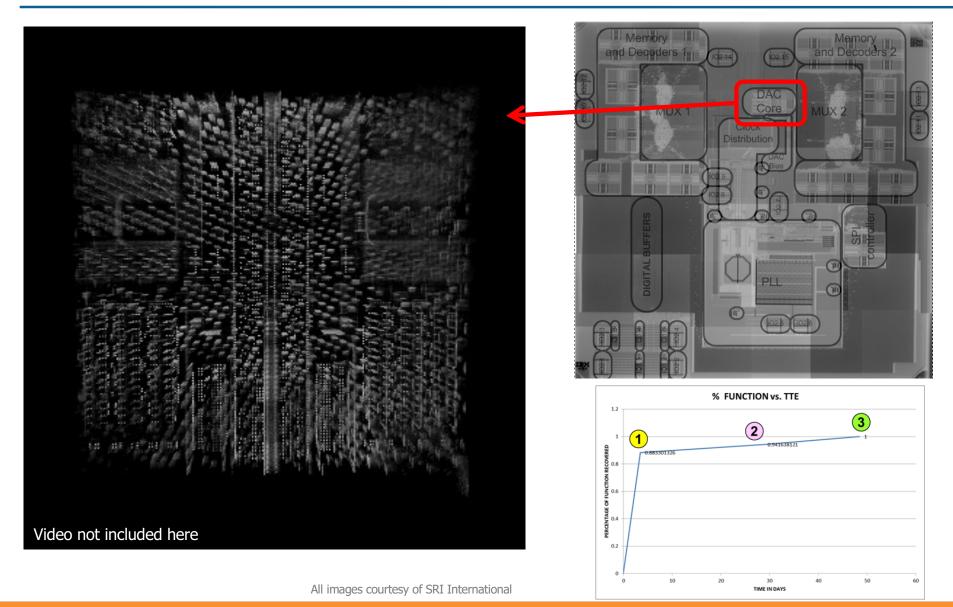

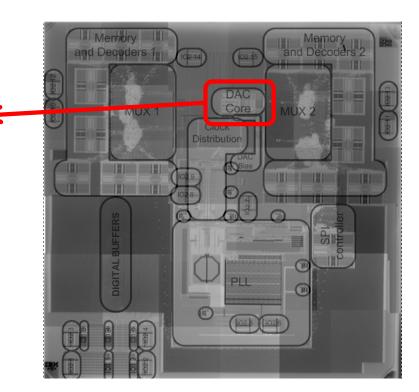

# DARPA 3D reconstruction of DAC – Non-destructive

#### **ENABLES 3D VISUALIZATION AND SPATIAL ANALYSIS**

All images courtesy of SRI International

HIGH RESOLUTION IN DEPTH ENABLES LAYER SEPARATION AND MEASUREMENT OF THICKNESS WITHOUT GRINDING

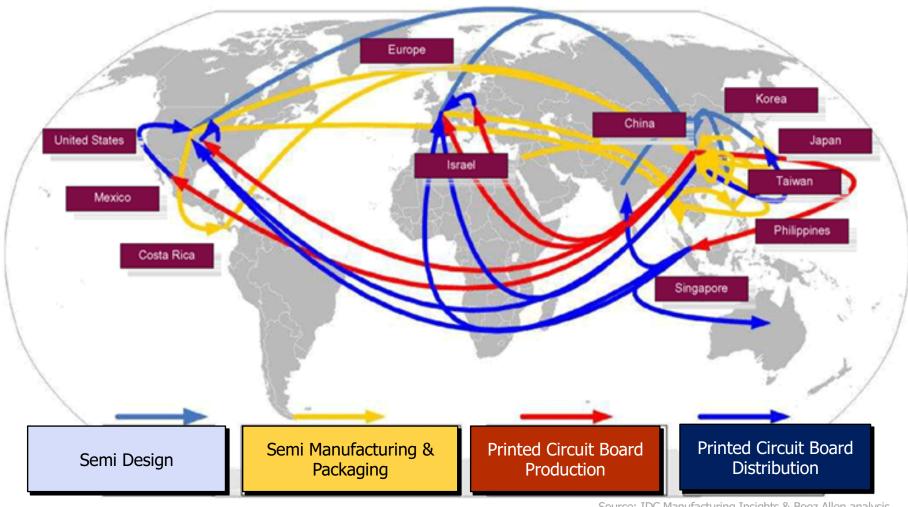

## The global nature of today's supply chains

#### Global nature of supply chain makes chain-of-custody unworkable

Source: IDC Manufacturing Insights & Booz Allen analysis

Lifecycle shown for a single Joint Strike Fighter component, which changes hands 15 times before final installation

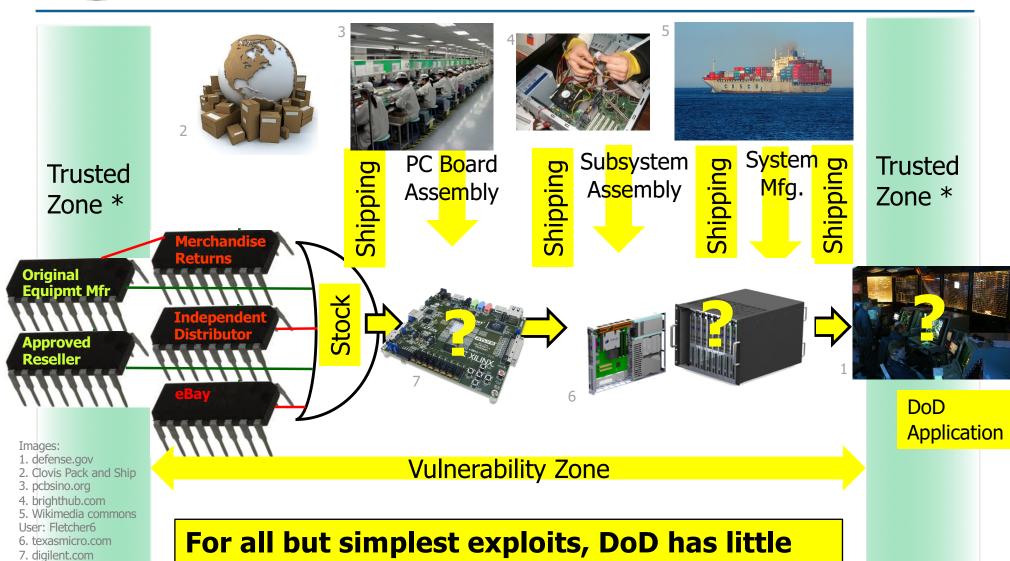

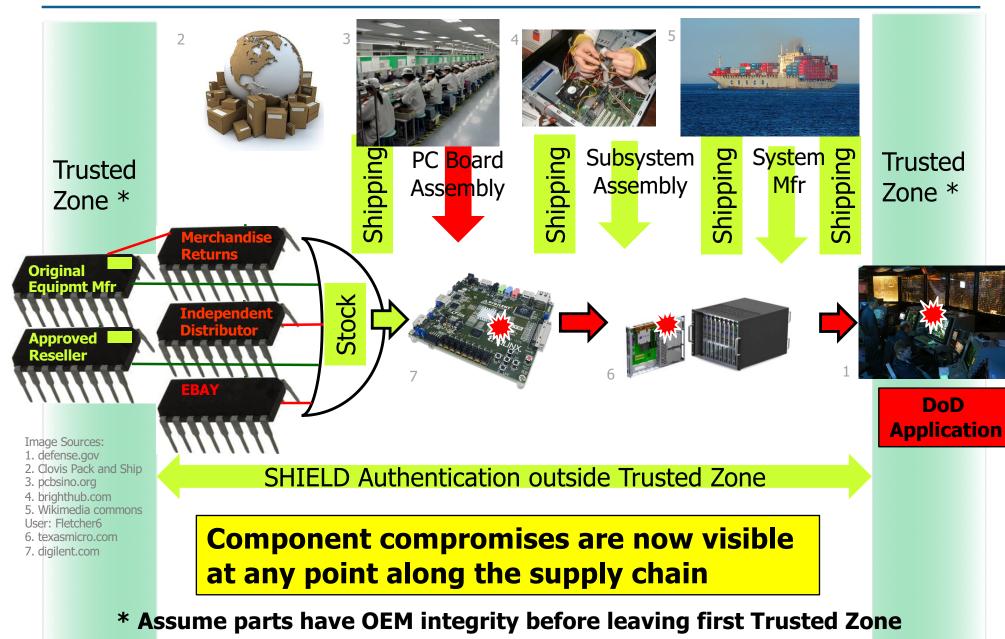

# Current untrusted logistical supply chain

For all but simplest exploits, DoD has little system component assurance of authenticity

\*Assume parts have OEM integrity before leaving first Trusted Zone

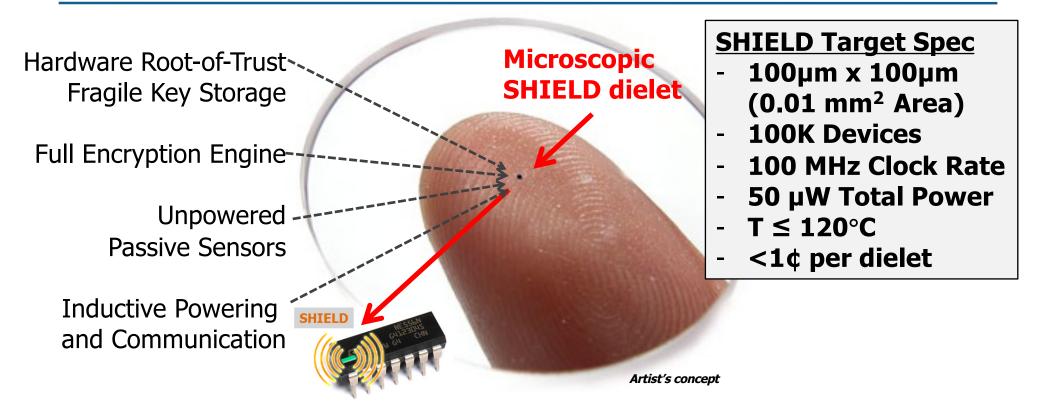

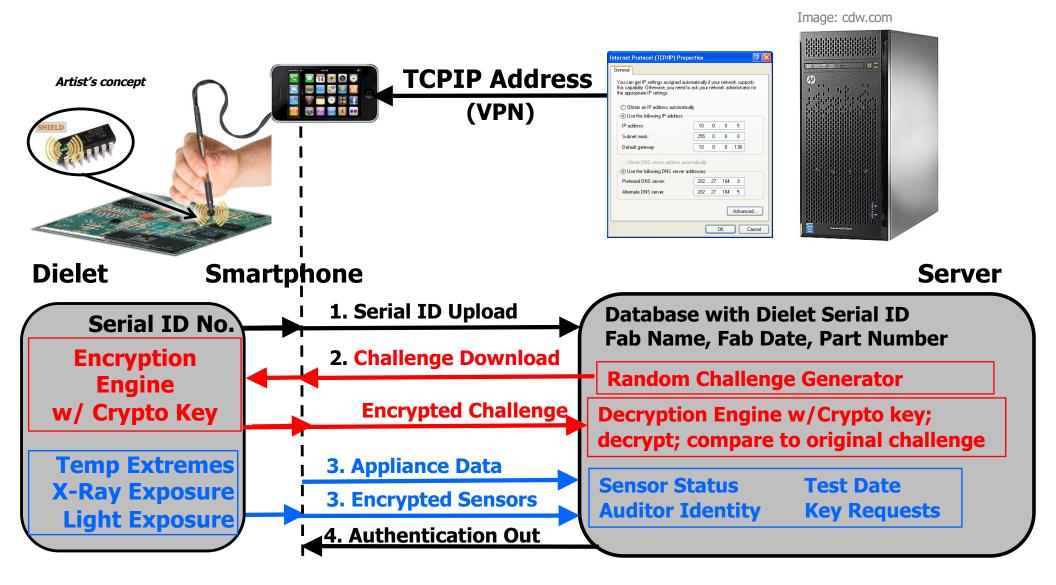

## SHIELD: DARPA's supply chain solution

DARPA SHIELD will develop the ability to provide nearly 100% assurance against certain known threat modes quickly, on demand, at any step of the supply chain, at extremely low cost.

SHIELD makes counterfeiting too expensive and too hard to do.

### **Example SHIELD CONOP**

# Revisiting the supply chain – now with SHIELD implementation

## What makes SHIELD "DARPA-worthy?"

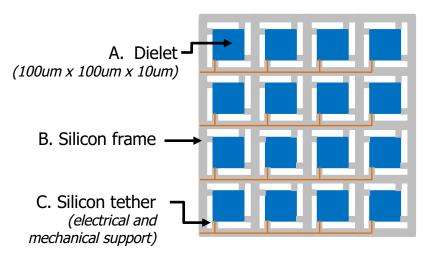

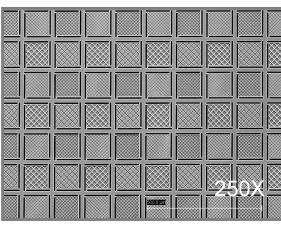

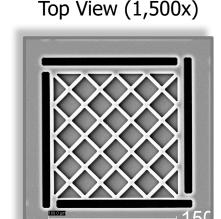

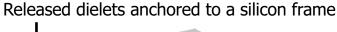

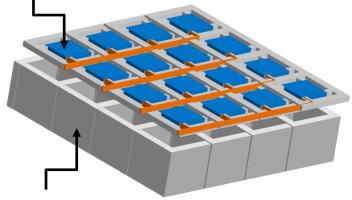

# At 100µm by 100µm by 10µm thick, the SHIELD dielet is on track to be the smallest integrated circuit ever developed

- Whole new technologies for building the "science of SMALL"

- Remote chip communication and powering using microscopic antennae

- Design of passive sensors that cannot be reset or inadvertently triggered

SHIELD dielet surrogate (SRI International)

Microscopic Sort and Pick (SRI International)

## Example technology - Draper fragility

Goal: design and develop a high-yield, low cost architecture for the fabrication, testing, and packaging of ultra-thin (<10µm) dielets with engineered fragility

Carrier wafer with etched cavities under individual dielets

Video not included here

Perspective View (10,000x)

G. Perlin, et al.

Images courtesy of Draper Laboratories

## Fab-of-Origin (ClearMark, Chromologic, IC Forensics)

- Fab-of-Origin looks for fab-signatures to identify origin of a component

- Idiosyncrasies associated with fab-specific tooling, recipe, sequence

- Needed to trace DoD, non-DoD clones and counterfeits to originating foundry (Smart Grid, Cyber Systems, Communications, etc...)

#### MTO SBIR SB133-03: Fab of Origin

http://mediad.publicbroadcasting.net/p/innovationtrail/files/201301/IMG\_0362.JPG

http://www.turbosquid.com/3d-models/c4d-factory-smoke/229722

Once SHIELD determines a chip to be a counterfeit, Fab-of-Origin will provide the insight needed to identify where it was made.

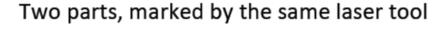

# Thinking "outside the box" Determining Fab-of-Origin

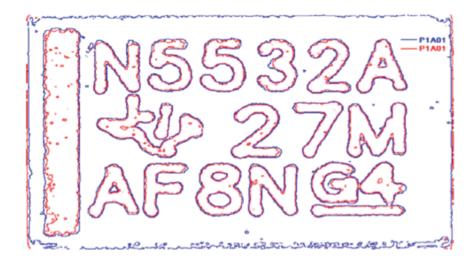

Two parts, marked by different laser tools in the same facility

Images compliments of Clearmark, Inc.

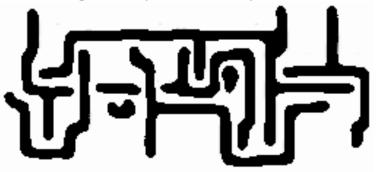

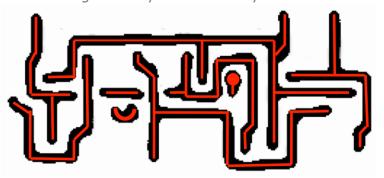

#### What characterizes the circuit layout of an ASIC?

Image courtesy of Air Force Research Laboratory

# Medium is (M1) metallization patterns in SEM image tiles

# Basis patterns are *unknown* cell designs from the standard library for the foundry

Image courtesy of Clearmark Systems

The layout information is contained in the line drawing of the patterns