#### **IARPA Trusted Integrated Chips (TIC) Program**

LEADING INTELLIGENCE INTEGRATION

Carl E. McCants, Ph.D. Program Manager 17 August 2016

# Outline

- Introduction

- TIC Program Details

- Summary

## Introduction

# Office of the Director of National Intelligence

# **IARPA Mission and Method**

IARPA's mission is to invest in high-risk/high-payoff research to provide the U.S. with an overwhelming intelligence advantage

## • Bring the best minds to bear on our problems

- Full and open competition to the greatest possible extent

- World-class, rotational Program Managers

## • Define and execute research programs that:

- Have goals that are clear, measureable, ambitious and credible

- Employ independent and rigorous Test & Evaluation

- Involve IC partners from start to finish

- Run from three to five years

- Publish peer-reviewed results and data, to the greatest possible extent

# **TIC Program Details**

# **TIC Program Vision**

- Ensure the U.S. Intelligence Community can obtain the highest performance possible in integrated circuit chips.

- Ensure capability, performance, and security of designs.

- Designs not compromised with malicious circuitry.

- Design intellectual property protected.

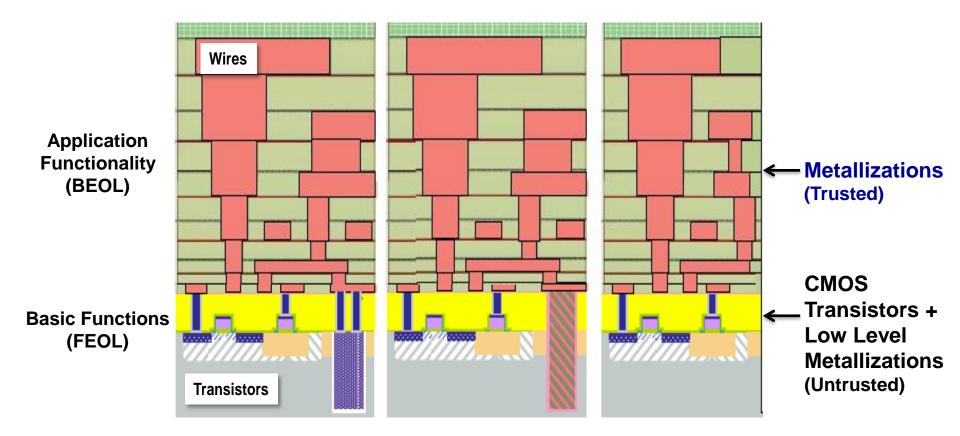

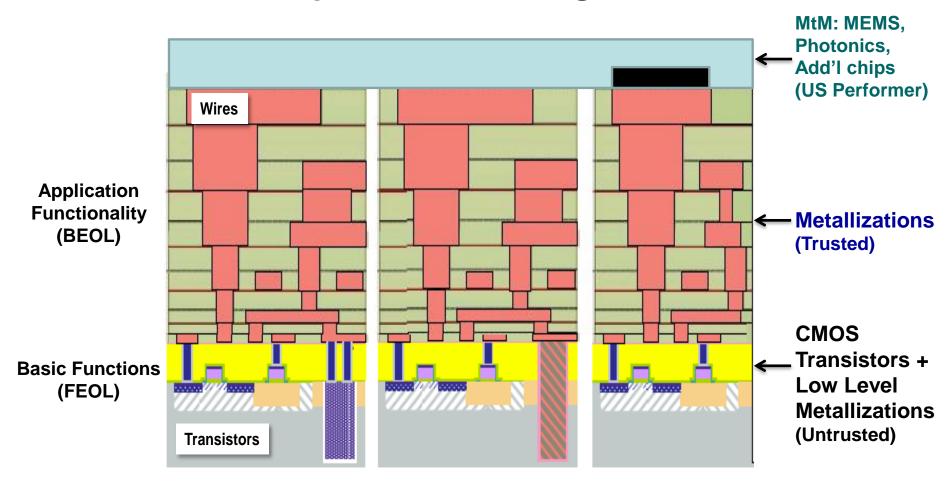

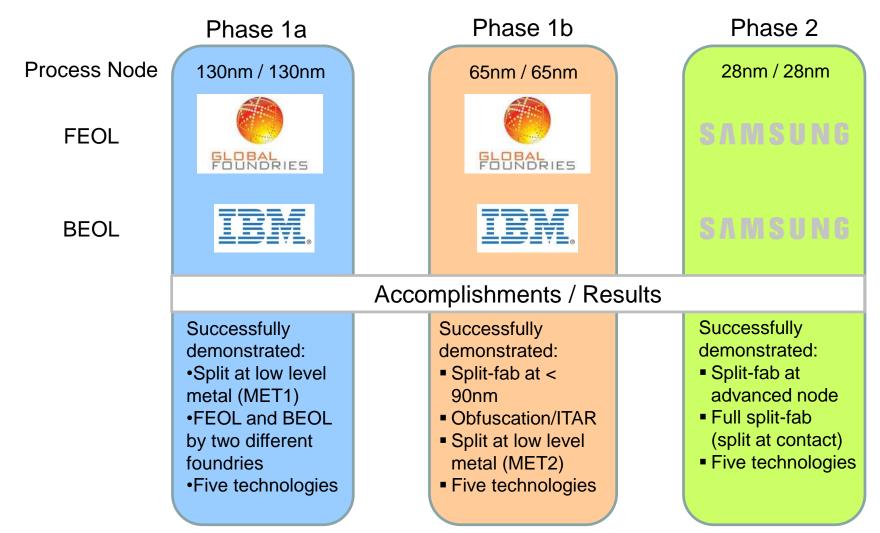

- Demonstrate split-manufacturing of chips using an advanced untrusted\* FEOL (Front End of Line) foundry and a trusted\* BEOL (Back End of Line) foundry.

\*Trust certification per current DMEA accreditation.

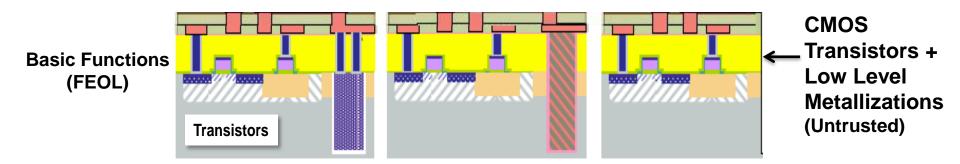

## **TIC Split-Manufacturing Process**

## **TIC Split-Manufacturing Process**

## **TIC Split-Manufacturing Process**

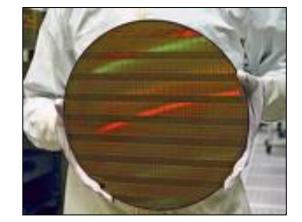

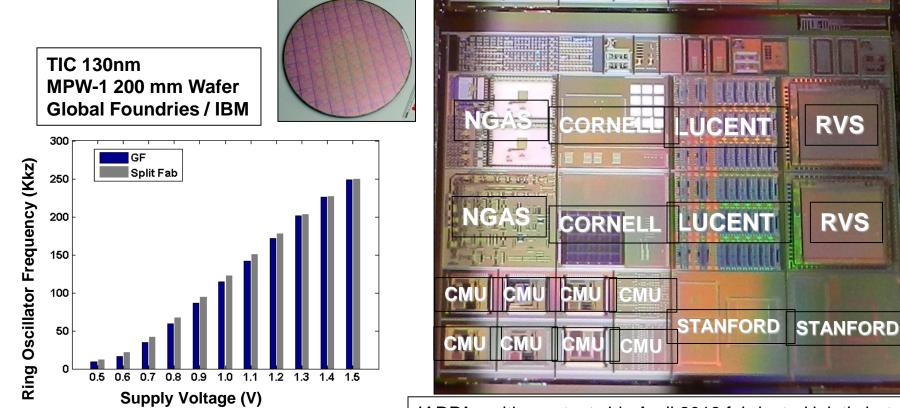

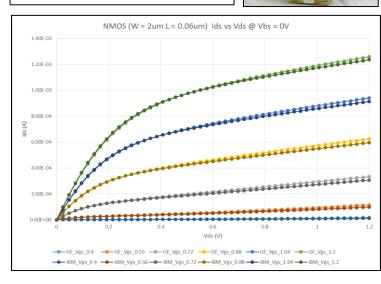

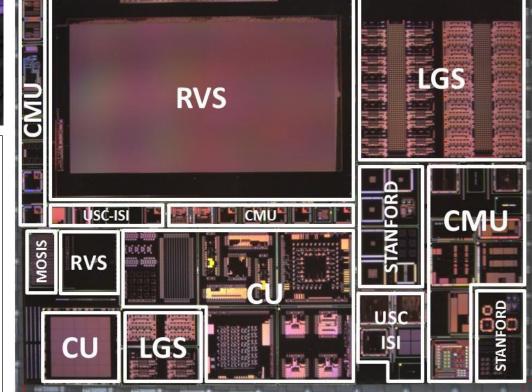

# **TIC 130 nm Wafer and Test Chips**

Split-manufactured integrated circuits in six different electronic families produced are fully functional and within process specification.

No significant difference in electrical performance.

IARPA multi-user test chip April 2013 fabricated jointly between Global Foundries (Singapore) and IBM (Burlington, VT).

# B

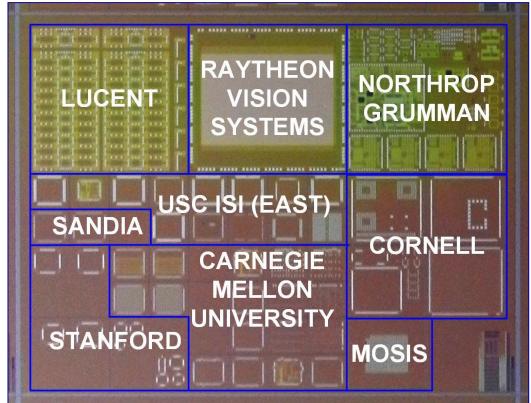

# **TIC 65 nm Wafer and Test Chips**

Split-manufactured integrated circuits show working circuits and are within process specification

#### TIC 65nm MPW-1 300 mm Wafer Global Foundries / IBM

No significant difference in electrical performance

IARPA multi-user test chip April 2014 fabricated jointly between Global Foundries (Singapore) and IBM (East Fishkill)

# **TIC 28 nm Wafer and Test Chips**

Split-manufactured integrated circuits with working circuits and are within process specification

#### TIC 28nm MPW 300 mm Wafer Samsung / Samsung

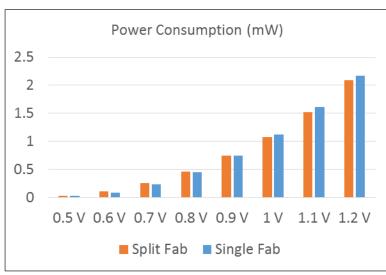

Power consumption for multiplier circuit.

No difference between split fab & reference.

IARPA multi-user test chip December 2015 fabricated jointly between Samsung (Korea) and Samsung (Austin).

# Phase 2 Final Program Results

| Metrics                                     |                        | OY 2<br>(18 mo) | СМИ           | Cornell       | LGS/Bell<br>Labs | RVS           | Stanford      |

|---------------------------------------------|------------------------|-----------------|---------------|---------------|------------------|---------------|---------------|

| Technology Node                             |                        | 28 nm<br>node   | 28 nm<br>node | 28 nm<br>node | 28 nm<br>node    | 28 nm<br>node | 28 nm<br>node |

| Circuit<br>Complexity (#<br>of transistors) | Digital                | >1M             | >3M           | 82.5M         | ~15M             | 1000M         | >1M           |

|                                             | Analog/Mixed<br>Signal | >1K             | >10K          | >30K          | ~14K             | >>1K          | na            |

| Split-Fabrication Yield                     |                        | >75%            | 100%          | 95%           | 78%              | 96%           | 95%           |

| Speed                                       |                        | >85%            | 100%          | 90%           | 86%              | *83%          | 95%           |

| Power Dissipation                           |                        | <120%           | 105%          | 104%          | 100%             | *92%          | 105%          |

CMU = Carnegie Mellon University RVS = Raytheon Vision Systems

\* For Phase 2, the speed and power curves for split and non-split devices overlap.

# **TIC Circuit Example**

# B

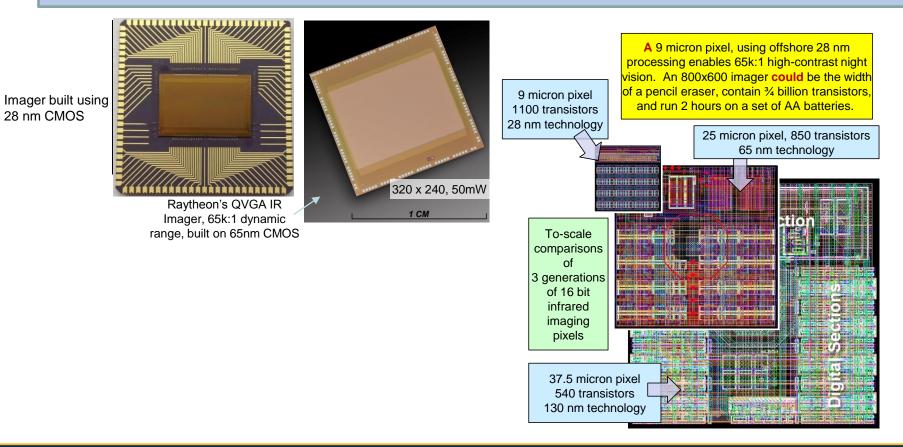

## **Raytheon Vision Systems**

#### **Raytheon**

**Goal:** Develop low size, weight and power <u>electro-optical sensors</u> by designing ROICs at advanced CMOS process nodes.

## Summary

# **TIC Program Major Accomplishments**

# **Questions?**